# Status of OTIS development

**Outer Tracker meeting**

LHCb week, 2001, may 7 —may 11

Harald Deppe , Martin Feuerstack -Raible , Uwe Stange , Andr Srowig Heidelberg University

#### **OTIS** submission overview

- Z DLL1.0, submitted september 2000, measurements in work (partly presented here)

- y First DLL prototype, contains

- x 32 stage delay chain with 32 taps

- x Mean delay per stage = 781ns nominal

- OTISDLL1.0, submitted february 28, 2001

- y 2nd DLL prototype, contains

- x 32 stage delay with 64 taps

- x Mean delay per tap = 390ns nominal

- OTISMEM1.0, submitted february 28, 2001

- y Contains rad hard L0 pipeline & derandomizer memory

- x 32 channels \* (1 + 6)bit/ch. + 16 bit = 240bit wide

- x 186 bit long

# DLL1.0 measurements(1)

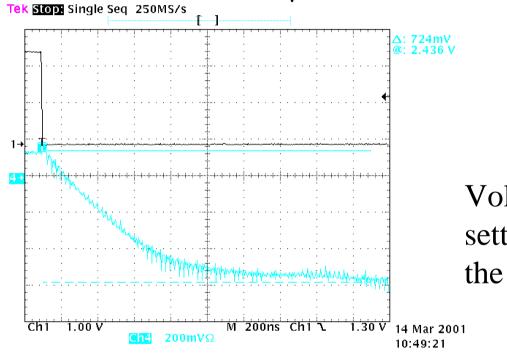

z Lock time is well below 2μs

Voltage controlling delay settles 2µs after reset of the circuit

Accidentally the lock gets lost and the DLL needs a reset

Y Not yet understood, maybe a problem in the test setup (e. g. switching on a neighbouring monitor causes loss of lock state), but operation of several hours w/o problems also possible.

## DLL1.0 measurements (2)

- Lock range = 22É 44MHz at 300K

- y Spec is 30É0MHz at 300K.

- y This is fully understood

- x an old W/L extraction rule for the transistors was used when the design was done

- x using the old layout with the new extraction rules yields an simulated lock range 20É 40MHz (within an 10% error)

- x OTISDLL1.0 layout has been corrected for lock range within specs

# **DLL1.0** measurements (1)

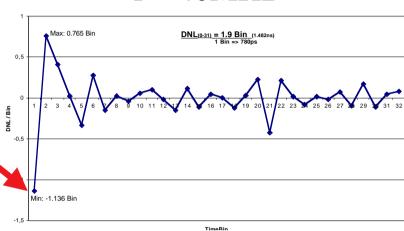

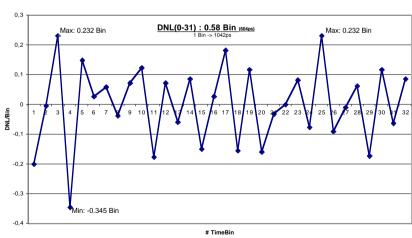

- Differential non-linearity (DNL)

- y 1.9bins at 40MHz

- x Large due to non-controlled dummy delay before first delay tap

- y 0.58bins at 30MHz (in the middle of the actual lock range, which fits better with the dummy delay)

- This translates to a resolution of

- y 1.482ns at 40MHz

- y 0.604ns at 30MHz

- Extrapolation to OTISDLL1.0

- y DNL = 0.58bins at 40MHz => resolution 0.45ns (within spec)

### **Next steps**

- OTISDLL1.0 and OTISMEM1.0 expected back in july 2001

- y Detailed measurements will be done asap

- Currently working on

- y behavioral model of the components

- y Overall design of chip OTIS1.0

- z Expect specification workshop in june